4-bit ALU

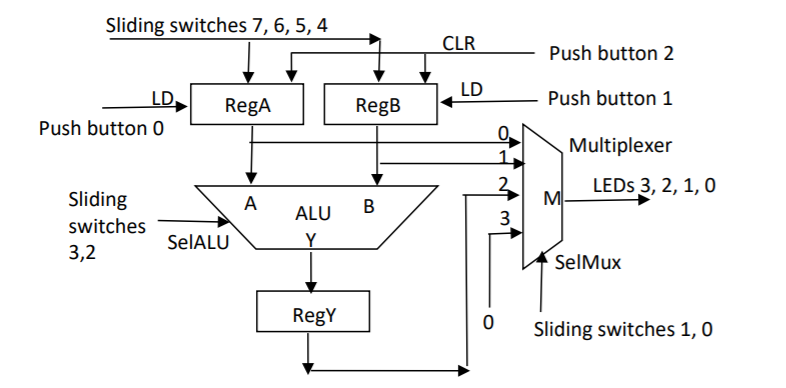

In EE361L we were tasked to program the Artix-7 Digilent Basys3 Board to perform the operations of a 4-bit arithmetic logic unit. This was done by using several SystemVerilog modules, with each module being used by the top module to complete each instruction. There were three component modules. The register, ALU, and multiplexer. Using temporary variables the top module would take inputs from each module to respond our desired output.

In this lab I was responsible for making the register module and contributing to the top module. Each of the component modules were provided through logic tables so it was just a matter of writing them in SystemVerilog.

From this project I learned more about coding in a team. While this work was done in a pair it was convenient to get all the small work of the components in a timely fashion by dividing the work. It was also important to communicate while troubleshooting the top module because when we hit a wall, we found a solution by talking through our thought processes. This highlighted that working in a team is all about communication.

You can learn more from the lab report here.